Translation Lookaside Buffer (TLB)

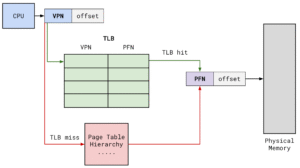

When using paging, every time the CPU accesses memory, it must first convert a logical address into a physical address by referring to the page table. But if this process happens for every memory access, it becomes slow—especially in multi-level paging systems. That’s where the Translation Lookaside Buffer (TLB) comes in.

The TLB is a specialized, high-speed cache that stores recent translations from virtual (logical) to physical addresses. It acts like a shortcut that helps avoid repeated and time-consuming page table lookups.

What is a TLB?

The Translation Lookaside Buffer is a small, fast memory component that holds a limited number of page table entries. It is part of the Memory Management Unit (MMU) in the CPU.

- The TLB caches recently used mappings from page numbers to frame numbers.

- When a logical address is generated, the system first checks the TLB before consulting the page table.

- If the mapping is found in the TLB, the physical address can be obtained very quickly.

How TLB Works

Here’s what happens during memory access:

- CPU generates a logical address.

- The MMU checks the TLB for a matching page number.

- If found (TLB hit), it retrieves the frame number instantly.

- If not found (TLB miss), it accesses the full page table, retrieves the frame number, and updates the TLB with this new mapping.

TLB Hit vs. TLB Miss

- TLB Hit:

The required page-frame mapping is found in the TLB. This results in fast access, and the CPU proceeds to fetch the data quickly.

- TLB Miss:

The mapping is not found in the TLB. The system then looks it up in the page table, which is slower. Once found, it is inserted into the TLB for future use.

TLB Characteristics

- Limited size (typically 64 to a few hundred entries).

- Works on the principle of temporal locality—pages used recently are likely to be used again.

- Uses replacement policies like Least Recently Used (LRU) to manage its entries.

- Modern CPUs often have separate TLBs for instructions and data (called split TLBs).

Why TLBs Are Important

- Improves Speed: Reduces the time spent on address translation.

- Minimizes Memory Access Delay: Especially important in systems using multi-level paging.

- Enhances Performance: Reduces the average memory access time for programs.

In real-world operating systems, TLBs are vital for keeping up with the performance demands of multitasking and large applications.